## CHAIN® Network Adapter User Guide

#### License

© 2008 Silistix, All Rights Reserved.

This document, including all software and software described in it, is furnished under the terms of the CHAIN Documentation License Agreement (the "License") and may only be used or copied in accordance with the terms of the License. The information in this document is a work in progress, developed by Silistix, and is furnished for informational use only.

The technology disclosed herein may be protected by one or more patents, copyrights, trademarks and/or trade secrets owned by or licensed to Silistix. Silistix reserves all rights with respect to such technology and related materials. Any use of the protected technology and related material beyond the terms of the License without the prior written consent of Silistix is prohibited.

This document contains material that is confidential to Silistix and its licensors. The user should assume that all materials contained and/or referenced in this document are confidential and proprietary unless otherwise indicated or apparent from the nature of such materials (for example, references to publicly available forms or documents). Disclosure or use of this document or any material contained herein, other than as expressly permitted, is prohibited without the prior written consent of Silistix or such other party that may grant permission to use its proprietary material.

The trademarks, logos, and service marks displayed in this document are the registered and unregistered trademarks of Silistix.

The copyright and trademarks owned by Silistix, whether registered or unregistered, may not be used in connection with any product or service that is not owned, approved or distributed by Silistix, and may not be used in any manner that is likely to cause customer confusion or that disparages Silistix. Nothing contained in this document should be construed as granting by implication, estoppel, or otherwise, any license or right to use any copyright without the express written consent of Silistix, its licensors or a third party owner of any such trademark.

#### Disclaimer

Except as otherwise expressly provided, this specification and any other documentation is provided by Silistix to users "as is" without warranty of any kind, express, implied or statutory, including but not limited to any implied warranties of merchantability, fitness for a particular purpose and non-infringement of third party rights.

Silistix shall not be liable for any direct, indirect, incidental, special or consequential damages of any kind or nature whatsoever (including, without limitation, any damages arising from loss of use or lost business, revenue, profits, data or goodwill) arising in connection with any infringement claims by third parties or the specification, whether in an action in contract, tort, strict liability, negligence, or any other theory, even if advised of the possibility of such damages.

## **Table of Contents**

| ADAPTER BASICS: CONNECTING HARDWARE IP TO THE SIL      | ISTIX <b>N</b> ETWORK-ON- |

|--------------------------------------------------------|---------------------------|

| CHIP (NoC)                                             |                           |

| What is an Adapter?                                    | 7                         |

| Initiator Adapters                                     | 7                         |

| Target                                                 | 8                         |

| Declaring Adapter-specific Options in CSL              | 9                         |

| Related Documents                                      | 9                         |

|                                                        |                           |

| AMBA PERIPHERAL BUS (APB) ADAPTER                      |                           |

| General Attributes                                     | 11                        |

| Protocol Version                                       | 12                        |

| Endian                                                 | 12                        |

| Address Bus Width                                      | 12                        |

| Data Bus Width                                         | 12                        |

| APB Version 3 Options                                  | 12                        |

| Write Error Control                                    | 12                        |

| Read Error Control                                     | 12                        |

| Optional Pipeline Register Control                     | 13                        |

| APB-side Interface                                     | 13                        |

| CGP-side Interface                                     | 13                        |

| Advanced Options                                       | 13                        |

| Target Data Width Wider than Initiator                 | 13                        |

| Multiported Endpoint Multiplexer/Demultiplexer Control | 14                        |

| More Information                                       | 15                        |

| AMPA HIGH COSED BUG (AHB) ADARTED                      | 47                        |

| AMBA HIGH-SPEED BUS (AHB) ADAPTER                      |                           |

| General Attributes                                     |                           |

| Protocol Version                                       |                           |

| Endian                                                 |                           |

| Address Bus Width                                      |                           |

| Data Bus Width                                         |                           |

| Initiator-Only Attributes                              |                           |

| HLOCK Support                                          | 19                        |

| Error Handling and Reporting                           | 20                        |

| Optional Pipeline Register Control                     | 20                        |

| AHB-side Interface                                     | 20                        |

| CGP-side Interface                                     | 20                        |

| More Information                                       | 21                        |

| AMBA ADVANCED EXTENSIBLE INTERFACE (AXI) ADAPTEI | R23        |

|--------------------------------------------------|------------|

| General Attributes                               | 23         |

| Endian                                           | 23         |

| Address Bus Width                                | 23         |

| Data Bus Width                                   | 23         |

| ID Bit Width                                     | 23         |

| Optional Pipeline Register Control               | 26         |

| AXI-side Interface                               | 26         |

| CGP-side Interface                               | 26         |

| Initiator Outstanding Transactions Control       | 27         |

| Allowable IDs                                    | 27         |

| Allowable ID Instances                           | 27         |

| Maximum Number of Outstanding Transactions       | 27         |

| Target Write Interleave Control                  | 27         |

| More Information                                 |            |

|                                                  |            |

| OPEN CORE PROTOCOL (OCP) ADAPTER                 | 29         |

| OCP Signal Groups                                | 29         |

| OCP Attributes                                   | 29         |

| Protocol Attributes                              | 29         |

| Phase Attributes                                 | 30         |

| Signal Attributes                                | 30         |

| Basic Signals                                    | 30         |

| General Attributes                               | 33         |

| Endian                                           |            |

| Basic Interface Signals                          |            |

| Address Bus Width                                |            |

| Data Bus Width                                   |            |

| Optional Pipeline Register Control               | 34         |

| OCP-side Interface                               |            |

| CGP-side Interface                               |            |

| Simple Extensions                                |            |

| Address Space Width                              |            |

| MDataInfo Width                                  |            |

| MRegInfo Width                                   |            |

| SDataInfo Width                                  |            |

| SRespInfo Width                                  |            |

| Burst Extensions                                 |            |

| Tag Extensions                                   |            |

| Thread Extensions                                |            |

| THI COM EXCUISIONS                               | ······ 4 I |

| Sideband Signals                          | 42 |

|-------------------------------------------|----|

| Test Signals                              | 43 |

| OCP Core RTL Configuration Files          |    |

| Default Initiator Adapter                 | 44 |

| Default Target Adapter                    | 45 |

| Initiator Adapter for MIP32-24K Processor |    |

| More Information                          | 47 |

| GLOSSARY                                  | 48 |

| Revision History                          | 49 |

| Feedback                                  | 49 |

## [ THIS PAGE INTENTIONALLY LEFT BLANK ]

# Adapter Basics: Connecting Hardware IP to the Silistix Network-on-Chip (NoC)

## What is an Adapter?

A Silistix adapter connects IP blocks in the system, based on one of the industry-standard interfaces shown in Table 1, to the Silistix CHAIN Network-on-Chip (NoC) architecture. The Silistix adapter provides all the necessary data protocol conversion and formatting.

IP Standard Initiator Target

AMBA APB N/A

AMBA AHB

AMBA AXI

OCP

Table 1: Silistix NoC Adapters (May 2008)

Each Silistix adapter is clocked using the same local or regional clock source that drives the attached hardware IP block. However, once converted, all traffic over the Silistix Network-on-Chip is self-timed and asynchronous.

Adapters are available as either an initiator or a target, per IP standard listed in Table 1. AMBA APB, however, is only defined as a target.

## **Initiator Adapters**

Figure 1 presents a top-level diagram of how an initiator IP block attaches to the Silistix NoC using a Silistix network adapter. When the IP block wishes to initiate a transaction, it generates any command, address, and data as might be required by the native IP interface protocol. The Silistix initiator adapter converts this request into an internal form called Protocol Mapping Format (PMF). The PMF format enables nearly transparent transactions between different IP interface standards. These PMF packets then tunnel through the Silistix Chain Gateway Protocol (CGP) network.

The initiator adapter also decodes the address for any transaction so that packets are correctly routed to their proper destination.

The addressed target at the other end of the network responds to commands sent by the initiator. Its response returns over the CGP network as PMF packets. The initiator adapter reconverts these PMF packets into the native protocol understood by the initiator IP block.

In some applications, the initiator adapter also reshapes data packets. For example, if a 64-bit initiator communicates to an 8-bit target, then the adapter converts each 64-bit transaction into eight byte-wide transactions.

Figure 1: Example Initiator Adapter Silistix NoC Adapter **Initiator IP Block** Address Decoder Optional Optional Proprietary or Convert standard 3<sup>rd</sup>-Party Command Command **IP Block** Register Register Chain Silistix History Buffer, Gateway **CHAIN** Resphaping **Protocol** Network Standards-Based Optional Optional **Interface** Response Response ■ AMBA AHB Register **Convert PMF to** ■ AMBA AXI standard ■ OCP PMF = Protocol Mapping Format

Because both the initiator and target IP blocks communicate through the Silistix network, they can have the same or completely different native formats, courtesy of the Silistix Protocol Mapping Format (PMF). For example, an OCP-based initiator can communicate with an APB-based target.

The History Buffer tracks and manages any potential outstanding requests. Some of the protocol adapters, such as AXI, allow there to be multiple outstanding transactions on the network.

## **Target**

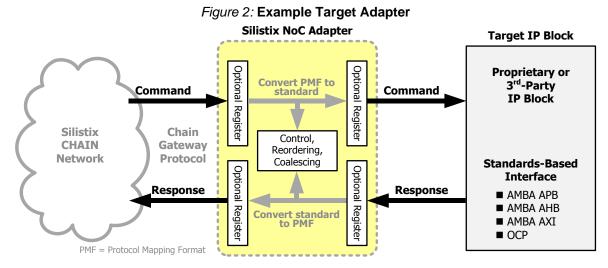

Figure 2 presents a top-level diagram of how a target IP block attaches to the Silistix NoC using a Silistix network adapter. The address decoding for the target, as well as the any transaction arbitration, is seamlessly handled within the Silistix network.

The addressed target responds to the command sent by the transaction initiator. The adapter converts the command, sent in PMF, into the native protocol supported by the IP block. The response from the target, converted back into PMF packets, is sent back to the initiator over the Silistix CGP network. The initiator adapter at the other end of the network converts these PMF packets into the native protocol understood by the initiator IP block.

In some applications, the target adapter also performs data reordering, trimming, or coalescing functions.

## **Declaring Adapter-specific Options in CSL**

Generally, there is no need to specify an adapter-specific option unless the application requires a value different than the default. However, there are also mandatory options for some protocol adapters. For example, the AXI adapter requires a setting to control the width of the AXI ID signals. As shown in Figure 3, these adapter-specific options can be included with the other statements in the CSL source file.

Figure 3: Adapter-specific Options Declared in CSL Source File

```

clock_domain cpu_domain (400 MHz) {

CPU_endpoint {

protocol = "AXI";

initiator CPU_initiator {

address = 32 bits;

data = 32 bits;

address_map = CPU_address;

write_response = 15 ns;

read_response = 30 ns;

// adapter-specific options

axi_id_bits = 1;

} //end CPU_initiator

target CPU_mailbox {

address = 4 bits;

data = 16 bits:

burstsize = 16 bytes;

address_range = COMM_address.CPU_mailbox;

// adapter-specific options

axi_id_bits = 1;

axi_write_interleave_depth = 1:

} // end CPU_mailbox target

// end CPU_endpoint

/ end clock_domain

```

#### **Related Documents**

Please refer to the following documents for additional information on how to use the CSL language to describe a system and how to process the design using the Silistix CHAINarchitect software.

- Building and Analyzing On-Chip Networks using CHAINarchitect

- Describing a System Using Connection Specification Language (CSL<sup>TM</sup>)

- CSL Language Reference Manual

## [ THIS PAGE INTENTIONALLY LEFT BLANK ]

## AMBA Peripheral Bus (APB) Adapter

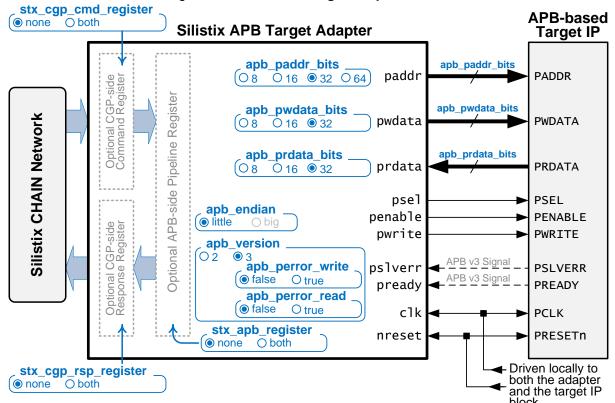

The Silistix APB adapter, shown in Figure 4, is designed according to the ARM AMBA Peripheral Bus standard. The AMBA Peripheral Bus (APB) is only supported as a target.

The APB adapter supports both version 2 and 3 of the protocol. Version 3 of the protocol adds the **PREADY** signal and the **PSLVERR** signal.

Support for multiported APB targets is provided in the adapter.

Customize the APB target adapter as required for the specific application by setting the attributes described below and summarized in Table 2.

Figure 4: Silistix APB Target Adapter and Attributes

The **PCLK** clock signal to the target IP block also drives the clocked logic within the APB target adapter. Similarly, the target adapter is reset by the active-Low **PRESETn** signal.

#### **General Attributes**

The following attributes are those that apply to all APB target applications. The name of each attribute is listed along with the allowable values. The default setting for the attribute appears in **Bold Underline**.

#### **Protocol Version**

The **apb\_version** attribute defines which version of the interface is generated. The primary difference is that version 3 adds the **PREADY** signal and the **PSLVERR** signal.

```

apb_version = { 2 | 3 }

```

When using version 3, all see the APB Version 3 Options section on page 12.

#### **Endian**

The current APB target adapter only supports little endian data ordering.

```

apb_endian = { little }

```

#### Address Bus Width

The **apb\_paddr\_bits** attribute defines the width of the APB address bus, measured in bits.

```

apb_paddr_bits = { 8 | 16 | 32 | 64 }

```

#### Data Bus Width

The APB interface has separate read and write data busses. The bit width of each data bus is independently defined using the **apb\_prdata\_bits** and **apb\_pwdata\_bits** attributes.

Read Data Bus Width

```

apb_prdata_bits = { 8 | 16 | 32 }

Write Data Bus Width

apb_pwdata_bits = { 8 | 16 | 32 }

```

## **APB Version 3 Options**

When using version 3 of the APB interface (apb\_version = 3), then a set of attributes defines if the hardware IP block attached to the target adapter can generate an error response on the PSLVERR signal in response to a read or write operation. By default, both read and write operations do not report errors. By default, both read and write operations do not support error handling or reporting. If the attached target handles errors, set the write and read attributes true, as appropriate for the application.

#### Write Error Control

```

apb_perror_write = { false | true }

```

#### Read Error Control

```

apb_perror_read = { false | true }

```

Both attributes are automatically set to false if using version 2 of the APB interface  $(apb\_version = 2)$ .

12

## **Optional Pipeline Register Control**

As shown in Figure 4, pipeline registers are optionally available for both the CGP-side and the APB-side adapter interfaces. If inserted, then the register uses the same clock source as the APB target IP block. In general, the default setting of none is preferred.

#### APB-side Interface

By default, there are no additional pipelining registers on the APB interface signals. Set **stx\_apb\_register** = **both** to add a pipeline register to the inputs and outputs of the APB-side interface. Inserting these pipeline registers adds levels of latency.

```

stx_apb_register = { none | both }

```

#### CGP-side Interface

The CGP-side interface has both a command path and a response path. The command path includes address, command, or write operations from the initiator to the selected target. The response path includes any read or status responses from the selected target back to the initiator.

#### Command Path

By default, there is no additional pipelining registers on the CGP command interface signals. Set **stx\_cgp\_cmd\_register** = **both** to add a pipeline register to the inputs and outputs of the CGP-side command interface. Inserting these pipeline registers adds levels of latency.

```

stx_cgp_cmd_register = { none | both }

```

#### Response Path

By default, there is no additional pipelining registers on the CGP response interface signals. Set **stx\_cgp\_rsp\_register** = **both** to add a pipeline register to the inputs and outputs of the CGP-side response interface. Inserting these pipeline registers adds levels of latency.

```

stx_cgp_rsp_register = { none | both }

```

## **Advanced Options**

## Target Data Width Wider than Initiator

The following attributes control the adapter behavior when the data path width of the initiator is narrower than that of the APB target. The opposite case, where the initiator data path is wider than the target, is already handled by the initiator.

The target and initiator data values are aligned to the least-significant bit in the data word.

#### Write Data from Narrower Initiator to Wider Target

The stx\_apb\_narrow\_write and stx\_apb\_write\_burst\_concat attributes control the adapter behavior when an initiator with a narrower data width than the APB target IP writes data to the target. The stx\_apb\_write\_burst\_concat attribute defines whether or not the target adapter will attempt to combine beats of narrower burst into fewer beats of a wider burst. The stx\_apb\_narrow\_write attribute describes the behavior of the adapter when the burst is not of the correct width. Its options are either to zero pad the write data or to fail and return an error response. If the attribute stx\_apb\_write\_burst\_concat = true, then the stx\_apb\_narrow\_write attribute defines the adapter's behavior when it is unable to combine the beats of the burst into a wider transfer, perhaps because the burst is too short.

The **stx\_apb\_write\_burst\_concat** attribute defines whether a burst transfer from a narrower initiator is coalesced into one or more wider words for the wider APB target. There is additional area overhead when this attribute is set to **true**.

```

stx_apb_write_burst_concat = { false | true }

```

The **stx\_apb\_narrow\_write** attribute defines whether such an operation should cause the target to generate an error response on such an attempted write operation (the default), or if the more-significant data bits are padded with zeroes. This attribute prevents a mis-sized write operation.

```

stx_apb_narrow_write = { fail | zeropad }

```

#### Read Data from Wider Target back to Narrower Initiator

The adapter returns the correct bytes from the wider APB target, based on the address, back to the narrower initiator. Any excess, unaddressed data from the resulting target access is discarded because it is now requested by the initiator. This type of transaction is supported by default. If this attribute is set to fail, then the target generates an error response when a narrow read is attempted, preventing a mis-sized read operation.

```

stx_apb_narrow_read = { fail | supported }

```

## Multiported Endpoint Multiplexer/Demultiplexer Control

In a multiported application, a single adapter connects multiple APB targets. Read data from each target sub-port must be multiplexed together before returning to the initiator. Optionally, write data can be demultiplexed and presented to each target sub-port.

By default, these multiplexer and demulitiplexer functions are not implemented within the APB target adapter. However, the following options enable or disable these automatic functions in those applications that require the multiplexers and demultiplexer functions.

#### **Initiator Multiport Read**

When using a multi-ported APB interface, the **stx\_apb\_bridge\_multiport\_read** attribute defines whether the read multiplexer is automatically implemented within the adapter or manually defined within the target IP source code (the default).

```

stx_apb_bridge_multiport_read = { false | true }

```

#### **Initiator Multiport Write**

When using a multi-ported APB interface, the **stx\_apb\_bridge\_multiport\_write** attribute defines whether there is a signal write output port or multiple demultiplexed write output ports (the default).

```

stx_apb_bridge_multiport_write = { false | true }

```

Table 2: AMBA Peripheral Bus (APB) Adapter Attributes Summary

|                                                        |                             | Allowable          |                                                           |  |

|--------------------------------------------------------|-----------------------------|--------------------|-----------------------------------------------------------|--|

| Attribute Name                                         | Default                     | Values             | Description                                               |  |

| General Attributes                                     |                             |                    |                                                           |  |

| apb_version                                            | 3                           | 2, 3               | Protocol version                                          |  |

| apb_endian                                             | little                      | little             | Endian                                                    |  |

| apb_paddr_bits                                         | 32                          | 8, 16, 32, 64      | Address bus bit width                                     |  |

| apb_prdata_bits                                        | 32                          | 8, 16, 32          | Read data bus bit width                                   |  |

| apb_pwdata_bits                                        | 32                          | 8, 16, 32          | Write data but bit width                                  |  |

| APB Version 3 Options                                  |                             |                    |                                                           |  |

| apb_perror_read                                        | No default.                 | true, false        | Controls whether read errors                              |  |

| op.o_pos                                               | Must specify                |                    | supported on PSLVERR signal                               |  |

| apb_perror_write                                       | No default.<br>Must specify | true,false         | Controls whether write errors supported on PSLVERR signal |  |

| Optional Pipeline Register Con                         |                             |                    | supported on PSLVERK signal                               |  |

| stx_apb_register                                       | none                        | none, both         | Optional ABP-side pipeline register                       |  |

| Stx_apb_register                                       | Hone                        |                    | Optional CGP-side command                                 |  |

| stx_cgp_cmd_register                                   | none                        | none, both         | pipeline register.                                        |  |

| sty can rep register                                   | none                        | none, both         | Optional CGP-side response                                |  |

| stx_cgp_rsp_register                                   |                             | none, both         | pipeline register.                                        |  |

| Target Data Width Wider than I                         | nitiator                    |                    |                                                           |  |

| stx apb narrow write                                   | fail                        | fail,              | Behavior during a narrow write                            |  |

|                                                        |                             | zeropad            | operation.                                                |  |

| stx_apb_write_burst_concat                             | false                       | true, false        | Coalesce narrow initiator writes to wider target          |  |

| stx_apb_narrow_read                                    | supported                   | fail,<br>supported | Behavior during a narrow read operation.                  |  |

| Multiported Endpoint Multiplexer/Demultiplexer Control |                             |                    |                                                           |  |

|                                                        |                             |                    | Controls whether read multiplexer                         |  |

| stx_apb_bridge_multiport_read                          | false                       | true, false        | is in the adapter or the IP block.                        |  |

|                                                        |                             |                    | Controls whether write                                    |  |

| stx_apb_bridge_multiport_write                         | false                       | true, false        | demultiplexer is in the adapter or the IP block.          |  |

## **More Information**

The Silistix APB adapters were created according the APB 2.0 and APB 3.0 specifications available under license from ARM.

- AMBA 3 Specification www.arm.com/products/solutions/axi spec.html

- AMBA 2 Specification www.arm.com/products/solutions/AMBA\_Spec.html

## [ THIS PAGE INTENTIONALLY LEFT BLANK ]

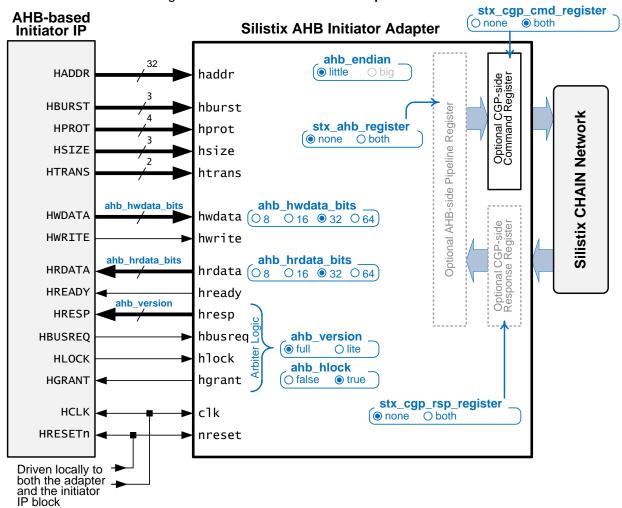

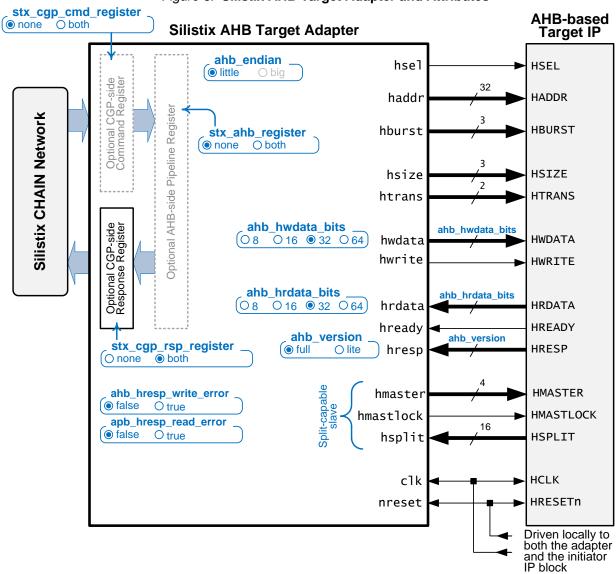

The Silistix AHB adapters are designed according to the ARM AMBA AHB standard.

The AHB adapters support both the full and lite versions of the specification.

Customize the AHB adapters as required for the specific application by setting the attributes described below and summarized in Table 6.

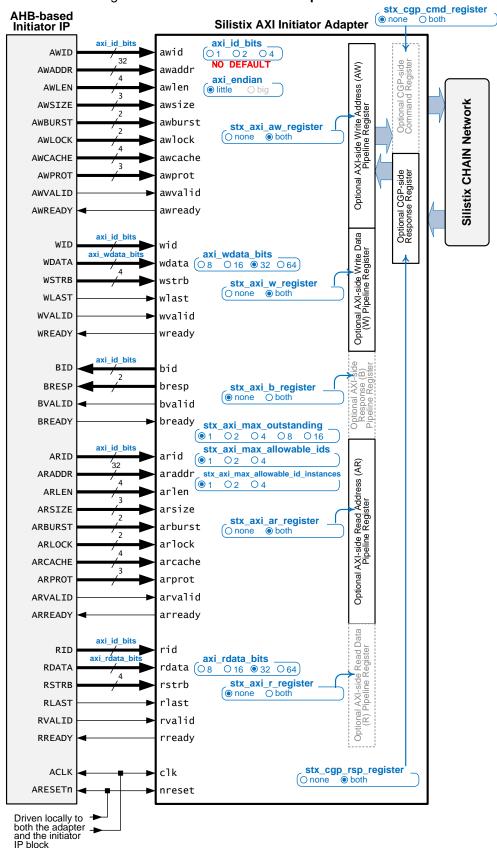

Both the AHB initiator and target adapters have the identical level of support. However, there are minor differences between the initiator and target. The initiator adapter, shown in Figure 5, has an additional attribute (abh\_hlock) and the target adapter, shown in Figure 6, has an additional signal (HSEL). Similarly, when the attribute ahb\_version = full, then the initiator adapter also includes the signals designed for a multi-master interface, including the HBURSTREQ and HGRANT signals. The target adapter does not have these signals.

The **HCLK** clock signal to the target IP block also drives the clocked logic within the AHB adapter. Similarly, the target adapter is reset by the active-Low **HRESETn** signal.

#### **General Attributes**

The following attributes apply to all AHB adapter applications. The name of each attribute is listed along with the allowable values. The default setting for the attribute appears in **Bold Underline**.

#### Protocol Version

The **ahb\_version** attribute defines which version of the interface is generated. The **full** version of the initiator adapter includes additional arbiter signals. The **lite** version of the initiator adapter is designed for a single-master system; the initiator arbiter signals are removed and the **HRESP** signal is reduced to a single bit for both the initiator and target adapters as shown in Table 3.

ahb\_version = { full | lite }

Table 3: AXI Full vs. Lite Signal Differences

|           | Full                                       | Lite  |

|-----------|--------------------------------------------|-------|

| Initiator | HRESP[1:0]<br>HBUSREQ<br>HLOCK<br>HGRANT   | HRESP |

| Target    | HRESP[1:0]<br>HMASTER[3:0]<br>HSPLIT[15:0] | HRESP |

#### **Endian**

The current AHB adapter only supports little endian data ordering.

```

ahb_endian = { little }

```

#### Address Bus Width

In the current implementation of the adapter, the AHB address bus, **HADDR**, is always 32 bits wide.

#### Data Bus Width

The AHB interface has separate read and write data busses. The bit width of each data bus is independently defined by the **ahb\_hrdata\_bits** and **ahb\_hwdata\_bits** attributes.

#### Read Data Bus Width

```

ahb_hrdata_bits = { 8 | 16 | 32 | 64 }

```

Write Data Bus Width

ahb\_hwdata\_bits = { 8 | 16 | 32 | 64 }

Figure 5: Silistix AHB Initiator Adapter and Attributes

Figure 6: Silistix AHB Target Adapter and Attributes

## **Initiator-Only Attributes**

The following attributes apply only to the AHB initiator adapter.

## **HLOCK Support**

The AHB initiator adapter supports locked transfers by default. To disable locked transfers, set the attribute **ahb\_hlock** = **false**.

The **abh\_hlock** attribute controls different adapter signals, depending on the setting of the **ahb\_version** attribute, as listed in Table 4.

Table 4: Signal Affected by ahb\_hlock Attribute

| ahb_version Attribute | Signal Controlled by ahb_hlock |

|-----------------------|--------------------------------|

| full                  | HLOCK                          |

| lite                  | HMASTLOCK                      |

## **Error Handling and Reporting**

A set of attributes, **ahb\_hresp\_write\_error** and **ahb\_hresp\_read\_error**, define whether the hardware IP block attached the adapter handles errors. For a target adapter, these attributes indicate if the attached target endpoint (IP) generates an error response on the **HRESP** signal in response to a read or write operation. For an initiator adapter, these attributes indicate if the attached initiator endpoint (IP) understands errors reported on the **HRESP** signal. By default, both read and write operations do not support error handling or reporting. If the attached target or initiator handles errors, set the write and read attributes **true**, as appropriate for the application.

Write Error Control

```

ahb_hresp_write_error = { false | true }

Read Error Control

ahb_hresp_read_error = { false | true }

```

## **Optional Pipeline Register Control**

As shown in Figure 4, pipeline registers are optionally available for both the CGP-side and the AHB-side adapter interfaces. If inserted, then the register uses the same clock source as the AHB IP block.

#### AHB-side Interface

By default, there is no additional pipelining registers on the AHB interface signals. Set **stx\_ahb\_register** = **both** to add a pipeline register to the inputs and outputs of the AHB-side interface. Inserting these pipeline registers adds levels of latency.

```

stx_ahb_register = { none | both }

```

#### CGP-side Interface

The CGP-side interface has both a command path and a response path. The command path includes address, command, or write operations from the initiator to the selected target. The response path includes any read or status responses from the selected target back to the initiator.

The CGP interface provides optional pipeline registers for both the command and response paths. Each register is individually controlled by an attribute as shown in Table 5. Setting the attribute to **both** inserts the pipeline registers to the associated signal group. Inserting these pipeline registers adds levels of latency.

To remove the pipeline registers, set the associated attribute to **none**.

Table 5: CCP-side Pipeline Attributes

| 222.2    |                           | Initiator     | Target        |

|----------|---------------------------|---------------|---------------|

| CGP Path | Pipeline Register Control | Default Value | Default Value |

| Command  | stx_cgp_cmd_register      | both          | none          |

| Response | stx_cgp_rsp_register      | none          | both          |

Table 6: AMBA High-speed Bus (AHB) Adapter Attributes Summary

| Attribute Name                     | Default     | Allowable<br>Values | Description                                                |

|------------------------------------|-------------|---------------------|------------------------------------------------------------|

| General Attributes                 |             |                     |                                                            |

| ahb_version                        | full        | full, lite          | Protocol version                                           |

| ahb_endian                         | little      | little              | Endian                                                     |

| ahb_haddr_bits                     | 32          | 32                  | Address bus bit width                                      |

| ahb_hrdata_bits                    | 32          | 8, 16, 32, 64       | Read data bus bit width                                    |

| ahb_hwdata_bits                    | 32          | 8, 16, 32, 64       | Write data but bit width                                   |

| Initiator-Only Attributes          |             |                     |                                                            |

| ahb_hlock                          | true        | true, false         | Allow locked transfers                                     |

| Error Handling and Reporting       |             |                     |                                                            |

| ahb_hresp_write_error              | false       | true, false         | Controls whether write errors supported on HRESP signal    |

| ahb_hresp_read_error               | false       | true, false         | Controls whether read errors are supported on HRESP signal |

| Optional Pipeline Register Control |             |                     |                                                            |

| stx_ahb_register                   | none        | none, both          | Optional AHB-side pipeline register                        |

| stx_cgp_cmd_register               | See Table 5 | none, both          | Optional CGP-side command pipeline register.               |

| stx_cgp_rsp_register               | See Table 5 | none, both          | Optional CGP-side response pipeline register.              |

## **More Information**

The Silistix AHB adapters were created according the AHB specifications available under license from ARM.

- AMBA 3 Specification www.arm.com/products/solutions/axi\_spec.html

- AMBA 2 Specification www.arm.com/products/solutions/AMBA\_Spec.html

## [ THIS PAGE INTENTIONALLY LEFT BLANK ]

The Silistix AXI adapters are designed according to the ARM AMBA AXI standard.

Customize the AXI adapters as required for the specific application by setting the attributes described below and summarized in Table 6.

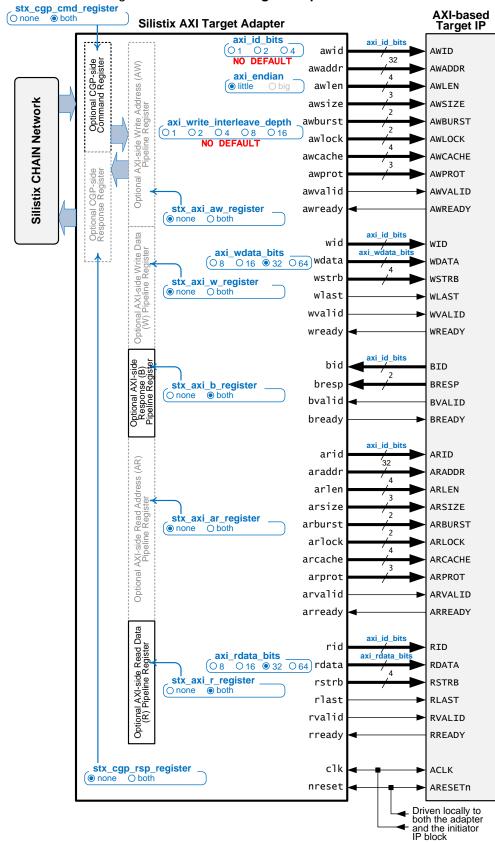

Both the AXI initiator adapter, Figure 7, and the target adapter, Figure 8, have an identical level of support.

#### **General Attributes**

The following attributes apply to all AXI adapter applications. The name of each attribute is listed along with the allowable values. The default setting for the attribute appears in **Bold Underline**.

#### Endian

The current AXI adapter only supports little endian data ordering.

```

axi_endian = { little }

```

#### Address Bus Width

In the current implementation of the adapter, the AXI address busses, **AWADDR** and **ARADDR**, are always 32 bits wide.

#### Data Bus Width

The AXI interface has separate read and write data busses. The bit width of each data bus is independently defined by the **axi\_rdata\_bits** and **axi\_wdata\_bits** attributes.

Read Data Bus Width

```

axi_rdata_bits = { 8 | 16 | 32 | 64}

Write Data Bus Width

axi_wdata_bits = { 8 | 16 | 32 | 64}

```

#### **ID** Bit Width

The AXI adapter optionally presents or accepts identification tags for each group of signals. The width of all the ID signals (AWID, WID, BID, and RID) is controlled by a single attribute, axi\_id\_bits. There is no default for this attribute so this mandatory value must be specified.

```

axi_id_bits = { 1 | 2 | 4 }

```

Figure 7: Silistix AXI Initiator Adapter and Attributes

Figure 8: Silistix AXI Target Adapter and Attributes

The **ACLK** clock signal to the target IP block also drives the clocked logic within the AXI adapter. Similarly, the target adapter is reset by the active-Low **ARESETn** signal.

## **Optional Pipeline Register Control**

As shown in Figure 7 and Figure 8, pipeline registers are optionally available for both the CGP-side and the AXI-side adapter interfaces. If inserted, then the register uses the same clock source as the AXI IP block.

#### **AXI-side Interface**

The AXI adapter provides optional pipeline registers for each of the AXI signal groups. Each register is individually controlled by an attribute as shown in Table 7. Setting the attribute to **both** inserts the pipeline registers into the associated signal group. Inserting these pipeline registers adds levels of latency.

To remove the pipeline registers, set the associated attribute to **none**.

**Initiator Target Pipeline Register Control** Signal Group/Channel **Default Value Default Value Write Address** stx\_axi\_aw\_register both none stx\_axi\_w\_register both Write Data none Write Response stx\_axi\_b\_register both none **Read Address** stx\_axi\_ar\_register both none **Read Data** stx\_axi\_r\_register none both

Table 7: AXI-side Pipeline Attributes

#### CGP-side Interface

The CGP-side interface has both a command path and a response path. The command path includes address, command, or write operations from the initiator to the selected target. The response path includes any read or status responses from the selected target back to the initiator.

The CGP interface provides optional pipeline registers for both the command and response paths. Each register is individually controlled by an attribute as shown in Table 8. Setting the attribute to **both** inserts the pipeline registers to the associated signal group. Inserting these pipeline registers adds levels of latency.

To remove the pipeline registers, set the associated attribute to **none**.

Table 8: CCP-side Pipeline Attributes

|          |                           | Initiator     | Target        |

|----------|---------------------------|---------------|---------------|

| CGP Path | Pipeline Register Control | Default Value | Default Value |

| Command  | stx_cgp_cmd_register      | none          | both          |

| Response | stx_cgp_rsp_register      | both          | none          |

## **Initiator Outstanding Transactions Control**

By default, the initiator adapter supports a single outstanding transaction. However, using the following advanced attributes, the initiator supports multiple unacknowledged outstanding transactions. Increasing the number of outstanding transactions generally improves performance but also increases the amount of silicon area consumed.

#### Allowable IDs

The AXI adapter **axi\_id\_bits** attribute defines how many unique AXI ID bits are supplied on the adapter interface. The **stx\_axi\_allowable\_ids** advanced attribute specifies how many different AXI IDs are allowed to have simultaneous outstanding transactions.

Setting this attribute lower saves area, but also impairs potential bus performance.

$$stx_axi_allowable_ids = \{ 1 | 2 | 4 \}$$

#### Allowable ID Instances

The **stx\_axi\_allowable\_id\_instances** advanced attribute specifies how many unique instances of a given AXI ID value are allowed to have simultaneous outstanding transactions.

Setting this attribute lower saves area, but also impairs potential bus performance.

$$stx_axi_allowable_id_instances = \{ 1 | 2 | 4 \}$$

## Maximum Number of Outstanding Transactions

The **stx\_axi\_max\_outstanding** advanced attribute specifies the maximum number of outstanding commands that the initiator is allowed to generate, regardless of the AXI ID.

Setting this attribute lower saves area, but also impairs potential bus performance.

$$stx_axi_max_outstanding = \{ 1 \mid 2 \mid 4 \mid 8 \mid 16 \}$$

## **Target Write Interleave Control**

Write data interleaving allows a target adapter to accept interleaved write data transfers with different AWID values. The mandatory **axi\_write\_interleave\_depth** attribute defines the write data interleaving depth that the adapter supports.

To avoid a deadlock condition, the **axi\_write\_interleave\_depth** attribute must be no larger than the maximum amount of interleaved write data that the target IP can continuously accept.

| Attribute Name     | Default | Allowable<br>Values | Description                 |

|--------------------|---------|---------------------|-----------------------------|

| General Attributes |         |                     |                             |

| axi_endian         | little  | little              | Endian                      |

| axi_raddr_bits     | 32      | 32                  | Read address bus bit width  |

| axi_waddr_bits     | 32      | 32                  | Write address bus bit width |

Table 9: AXI Adapter Attributes Summary

| Attribute Name                     | Default                    | Allowable<br>Values | Description                                                                            |  |

|------------------------------------|----------------------------|---------------------|----------------------------------------------------------------------------------------|--|

| axi_rdata_bits                     | 32                         | 8, 16, 32, 64       | Read data bus bit width                                                                |  |

| axi_wdata_bits                     | 32                         | 8, 16, 32, 64       | Write data bus bit width                                                               |  |

| axi_id_bits                        | No Default<br>Must specify | 1, 2, 4             | Width of ID signals                                                                    |  |

| Optional Pipeline Register Control |                            |                     |                                                                                        |  |

| stx_axi_aw_register                |                            | none, both          | Optional AXI-side pipeline register, Write Address channel                             |  |

| stx_axi_w_register                 |                            | none, both          | Optional AXI-side pipeline register, Write Data channel                                |  |

| stx_axi_b_register                 | See Table 7                | none, both          | Optional AXI-side pipeline register, Write Response channel                            |  |

| stx_axi_ar_register                |                            | none, both          | Optional AXI-side pipeline register, Read Address channel                              |  |

| stx_axi_r_register                 |                            | none, both          | Optional AXI-side pipeline register, Read Data channel                                 |  |

| stx_cgp_cmd_register               | See Table 8                | none, both          | Optional CGP-side command pipeline register                                            |  |

| stx_cgp_rsp_register               |                            | none, both          | Optional CGP-side response pipeline register                                           |  |

| Initiator Outstanding Transactions | Control                    |                     |                                                                                        |  |

| stx_axi_allowable_ids              | 1                          | 1, 2, 4             | Initiator only: Number of bursts, with different AXI IDs, allowed to be outstanding    |  |

| stx_axi_allowable_id_instances     | 1                          | 1, 2, 4             | Initiator only: Number of bursts, with same AXI ID, allowed to be outstanding          |  |

| stx_axi_max_outstanding            | 1                          | 1, 2, 4, 8, 16      | Initiator only: Maximum number of outstanding bursts allowed, regardless of the AXI ID |  |

| Target Write Interleave Control    |                            |                     |                                                                                        |  |

| axi_write_interleave_depth         | No Default<br>Must specify | 1, 2, 4, 8, 16      | Target only: Write interleave depth                                                    |  |

## **More Information**

The Silistix AXI adapters were created according the AXI specifications available under license from ARM.

- AMBA 3 Specification www.arm.com/products/solutions/axi\_spec.html

- AMBA 2 Specification www.arm.com/products/solutions/AMBA\_Spec.html

The Silistix OCP adapter is designed according to the Open Core Protocol (OCP) Specification, Release 2.2. Generally the OCP initiator and target adapters support similar features, although there are differences between the two as outlined below.

IP cores designed to OCP Release 1.0 are not supported.

The Silistix OCP attribute names are identical to those used in the OCP specification, except that they have an "ocp\_" prefix.

## **OCP Signal Groups**

The OCP interface specification divides the interface signals into a few simple categories, listed below. This chapter is similarly divided.

The OCP signal groups include the following.

- **Basic Signals**, which are generally required for any OCP interface.

- **Simple Extensions** that add more control signals and provide more information about each transfer.

- **Burst Extensions**, which allow grouping of multiple transfers that have a defined address relationship.

- **Tag Extensions** that tag data transfers for out-of-order responses and write data commit.

- Thread Extensions that add support for multi-threading of the OCP interface.

- Sideband Signals that contain signals that are not part of the dataflow phases.

- **Test Signals** that add support for scan, clock control, and IEEE 1149.1 (JTAG).

#### **OCP Attributes**

The Silistix OCP adapters are designed with the following OCP attribute settings.

#### Protocol Attributes

- The supported command enable attributes are described in the subsequent sections describing each OCP signal group

- ocp\_burst\_aligned = 0: There are no restrictions on INCR bursts. This is the OCP default.

- See "Burst Extensions" on page 38 for the supported burst sequence enable attributes.

- **ocp\_endian** = **little**: This is the OCP default.

- **ocp\_force\_aligned** = **0**: There are no restrictions on byte-enable signals. This is the OCP default.

- ocp\_mthreadbusy\_exact = 0, ocp\_sdatathreadbusy\_exact = 0, and ocp\_sthreadbusy\_exact = 0: The Silistix OCP adapters currently do not support multiple threads. This is the OCP default.

- ocp\_tag\_interleave\_size = 1: There are no restrictions on response interleaving. This is the OCP default.

#### Phase Attributes

- **ocp\_datahandshake** = 1: The datahandshake phase is always present. This is NOT the OCP default.

- **ocp\_reqdata\_together** = **0**: The first datahandshake phase is independent of the request phase. The initiator adapter may receive the first datahandshake phase in the same cycle as the request phase, or in a later cycle. The target adapter may issue the first datahandshake phase in the same cycle as the request phase, or in a later cycle.

- **ocp\_writeresp\_enable**: Both 0 and 1 are supported. The adapters optionally have responses enabled on write-type commands.

## Signal Attributes

The signal attribute settings are described in the subsequent sections describing each OCP signal group.

## **Basic Signals**

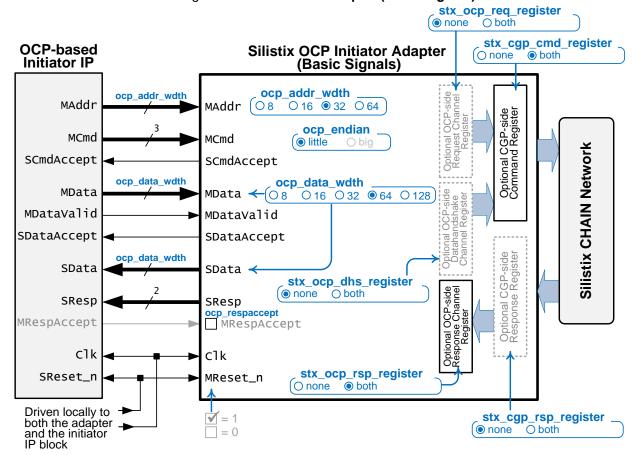

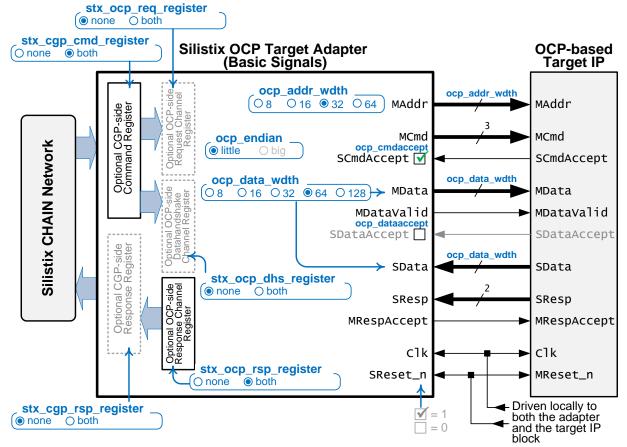

Generally OCP-based designs use most of the signals from the OCP basic signal group. The Silistix OCP adapters, shown in Figure 9 and Figure 10, support the basic signal group with the following characteristics and restrictions.

- The **Clk** signal is mandatory according to the OCP specification.

- The **EnableClk** signal is not supported. Consequently the attribute  $ocp_enableclk = 0$ .

- The MAddr signal is is supported and is mandatory (ocp\_addr = 1) for both initiator and target adapters. The behavior of the initiator adapter is undefined if it is issued a request with an unsupported address value on the MAddr signal. The initiator IP block must ensure that only supported addresses are issued to the adapter. Furthermore, the initiator IP block must align addresses presented on the MAddr signal to the data-word size, forcing the necessary numbers of lesser-significant address bits to zero.

- The **MCmd** signal is mandatory according to the OCP specification. Presently the OCP adapters support the IDLE, WR and RD commands on the **MCmd** signal. The initiator IP block must ensure that only the supported commands are issued to the adapter. The behavior of the initiator adapter is undefined if it receives an unsupported command. Furthermore, the OCP adapters must support both WR and RD commands. Therefore the only legal setting for the command enable attributes are as follows

| ocp_broadcast_enable    | 0 |

|-------------------------|---|

| ocp_rdlwrc_enable       | 0 |

| ocp_read_enable         | 1 |

| ocp_readex_enable       | 0 |

| ocp_write_enable        | 1 |

| ocp_writenonpost_enable | 0 |

- The **MData** signal is supported and is mandatory (**ocp\_mdata** = **1**) for both initiator and target adapters.

- The MDataValid signal is supported and is mandatory (ocp\_datahandshake = 1) for both initiator and target adapters.

- The MRespaccept signal is supported. It is optional (ocp\_respaccept = 0 or 1) for the initiator adapter and mandatory (ocp\_respaccept = 1) for the target adapter.

- The SCmdAccept signal is supported. It is mandatory (ocp\_cmdaccept = 1) for the initiator adapter and optional (ocp\_scmdaccept = 0 or 1) for the target adapter.

- The **SData** signal is supported and is mandatory (**ocp\_sdata** = **1**) for both initiator and target adapters.

- The SDataAccept signal is supported. It is mandatory ( $ocp_dataaccept = 1$ ) for the initiator adapter and optional ( $ocp_dataaccept = 0$  or 1) for the target adapter.

- The **SResp** signal is supported and is mandatory (**ocp\_resp** = **1**) for both initiator and target adapters. An OCP error is defined as when **SResp** = ERR in a response phase. The initiator adapter will NOT respond with an OCP error in the event of an unsupported request phase. It will only respond with **SResp** = ERR if the error was generated by the target IP block on the other side of the network. Supported encodings of **SResp** are NULL, DVA and ERR. The target IP block must ensure that only supported responses are issued to the target adapter.

The basic signals on an OCP initiator adapter appear in Figure 9. The MRespaccept signal is the only optional signal for the initiator adapter. The attribute name to enable or disable a particular interface signal appears directly above the associated check box in Figure 9.

Figure 9: OCP Initiator Adapter (Basic Signals)

The basic signals on an OCP target adapter appear in Figure 10. The **SCmdAccept** and **SDataAccept** signals are optional for the target adapter; all other signals are mandatory. The attribute name to enable or disable a particular interface signal appears directly above the associated check box in Figure 10.

Figure 10: OCP Target Adapter (Basic Signals)

#### **General Attributes**

The following attributes are those that apply to all OCP adapter applications. The name of each attribute is listed along with the allowable values. The default setting for the attribute appears in **Bold Underline**.

#### **Endian**

The current OCP adapters only support little endian data ordering.

## Basic Interface Signals

Some of the adapter basic interface signals are optional, controlled by individual enable or disable attributes as shown in Table 10.

Table 10: Basic Signal Attributes

| Interface Signal | Silistix Attribute | OCP<br>Parameter | Initiator<br>Default Value | Target<br>Default Value |

|------------------|--------------------|------------------|----------------------------|-------------------------|

| SCmdAccept       | ocp_cmdaccept      | cmdaccept        | 1<br>(mandatory)           | 1<br>(optional)         |

| SDataAccept      | ocp_dataaccept     | dataaccept       | 1<br>(mandatory)           | 0<br>(optional)         |

| MRespAccept      | ocp_respaccept     | respaccept       | 0<br>(optional)            | 1<br>(mandatory)        |

#### Address Bus Width

The **ocp\_addr\_wdth** attribute defines the width of the OCP address bus, measured in bits.

#### Data Bus Width

The OCP interface has separate read and write data busses but both have the same width. The **ocp\_data\_wdth** attribute defines the data bus bit width.

```

ocp_data_wdth = { 8 | 16 | 32 | 64 | 128 }

```

## **Optional Pipeline Register Control**

As shown in Figure 10, pipeline registers are optionally available for both the CGP-side and the OCP-side adapter interfaces. If inserted the register uses the same clock source as the OCP IP block.

#### **OCP-side Interface**

The OCP-side interface has separate Request, Response, and Datahandshake channels, each with individually-controlled, optional pipeline registers. The signals associated with each channel are listed in Table 11. Depending on other attribute settings, not all of the signals listed may be present on the interface.

#### Request Channel

By default there is no additional pipelining registers on the OCP request channel. Set **stx\_ocp\_req\_register = both** to add a pipeline register to the inputs and outputs of the OCP-side interface. Inserting these pipeline registers adds levels of latency.

```

stx_ocp_req_register = { none | both }

```

#### Datahandshake Channel

By default there are no pipelining registers present on the OCP datahandshake channel. Set **stx\_ocp\_dhs\_register** = **both** to add a pipeline register to the inputs and outputs of the OCP-side interface. Inserting these pipeline registers adds levels of latency.

```

stx_ocp_dhs_register = { none | both }

```

#### Response Channel

By default there are pipelining registers on both the inputs to and outputs from the OCP response channel. These pipeline registers add additional levels of latency. Set **stx\_ocp\_rsp\_register** = **none** to remove the pipeline registers.

```

stx_ocp_rsp_register = { none | both }

```

| Request Group                                                                                | Datahandshake Group                                                        | Response Group                                                  |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------|

| MAddr MAddrSpace MBurstLength MBurstSeq MBurstSingleReq MByteEn MConnID MCmd MReqInfo MTagID | MData<br>MDataByteEn<br>MDataInfo<br>MDataLast<br>MDataTagID<br>MDataValid | SData<br>SDataInfo<br>SResp<br>SRespInfo<br>SRespLast<br>STagID |

Table 11: OCP Phase Groups and Associated Signals on the Silistix Adapters

#### CGP-side Interface

The CGP-side interface has both a command path and a response path. The command path includes address, command, and write operations from the initiator to the selected target. The response path includes any read or status responses from the selected target back to the initiator.

#### Command Path

By default there are additional pipelining registers on the inputs and outputs of the CGP command interface signals. These pipeline registers add additional levels of latency. Set **stx\_cgp\_cmd\_register = none** to remove the pipeline registers.

#### Response Path

By default there are no additional pipelining registers on the CGP response interface signals. Set **stx\_cgp\_rsp\_register** = **both** to add a pipeline register to the inputs and outputs of the CGP-side response interface. Inserting these pipeline registers adds levels of latency.

```

stx_cgp_rsp_register = { none | both }

```

## **Simple Extensions**

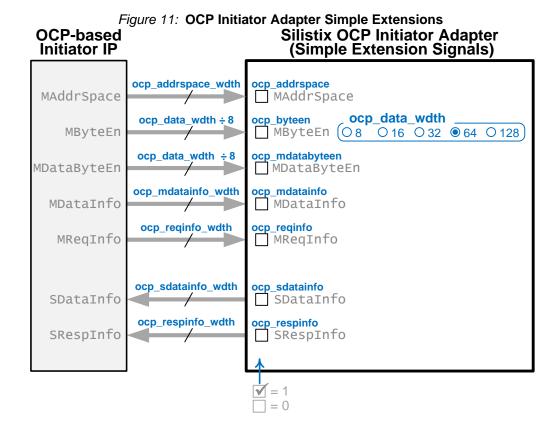

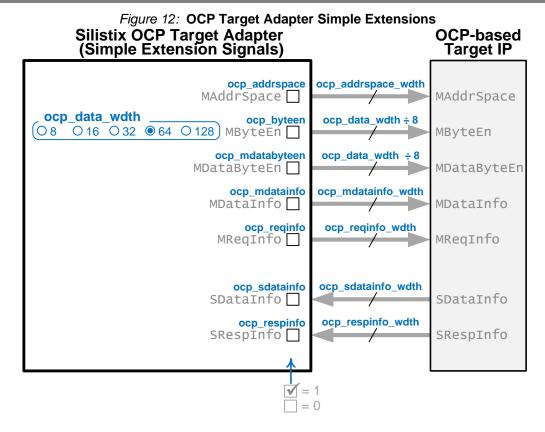

The OCP initiator and target adapters, shown in Figure 11 and Figure 12, support the simple extensions defined in the OCP specification, also listed in Table 12. None of the simple extension signals are enabled by default and must be individually enabled using associated attributes.

- The MAddrSpace signal is supported and is optional (ocp\_addrspace = 0 or 1) for both initiator and target adapters.

- The MByteEn signal is supported and is optional (ocp\_byteen = 0 or 1) for both initiator and target adapters.

- The MDataByteEn signal is supported and is optional (ocp\_mdatabyteen = 0 or 1) for both initiator and target adapters.

- The MDataInfo signal is supported and is optional (ocp\_mdatainfo = 0 or 1) for both initiator and target adapters.

- The MReqInfo signal is supported and is optional (ocp\_reqinfo = 0 or 1) for both initiator and target adapters.

- The **SDataInfo** signal is supported and is optional (**ocp\_sdatainfo** = **0** or **1**) for both initiator and target adapters.

- The **SRespInfo** signal is supported and is optional (**ocp\_respinfo** = **0** or **1**) for both initiator and target adapters.

The width of the **MByteEn** and **MDataByteEn** byte enable signals, if they are present on the interface, is defined by the **ocp\_data\_wdth** attribute divided by 8. In other words there is one individual byte enable signal for each byte in the data word.

The width of the other extension signals is controlled by associated, individual attributes as listed in Table 12.

Table 12: Simple Extensions Signal Attributes

| Interface<br>Signal | Silistix<br>Attribute | OCP<br>Parameter | Related Control(s)                            | Initiator<br>Default<br>Value | Target<br>Default<br>Value |

|---------------------|-----------------------|------------------|-----------------------------------------------|-------------------------------|----------------------------|

| MAddrSpace          | ocp_addrspace         | addrspace        | ocp_addrspace_wdth                            | 0                             | 0                          |

| MByteEn             | ocp_byteen            | byteen           | ocp_data_wdth                                 | 0                             | 0                          |

| MDataByteEn         | ocp_mdatabyteen       | mdatabyteen      | ocp_data_wdth                                 | 0                             | 0                          |

| MDataInfo           | ocp_mdatainfo         | mdatainfo        | ocp_mdatainfo_wdth,<br>ocp_mdatainfobyte_wdth | 0                             | 0                          |

| MReqInfo            | ocp_reqinfo           | reqinfo          | ocp_reqinfo_wdth,                             | 0                             | 0                          |

| SDataInfo           | ocp_sdatainfo         | sdatainfo        | ocp_sdatainfo_wdth,<br>ocp_sdatainfobyte_wdth | 0                             | 0                          |

| SRespInfo           | ocp_respinfo          | respinfo         | ocp_respinfo_wdth                             | 0                             | 0                          |

# Address Space Width

To add the MAddrSpace signal in the adapter interface, set the attribute ocp\_addrspace =  $\mathbf{1}$  and the ocp\_addrspace\_wdth attribute to an integer >  $\mathbf{0}$ .

#### MDataInfo Width

To add the **MDataInfo** signal in the adapter interface, set the attribute **ocp\_mdatainfo** = **1** and the **ocp\_mdatainfo\_wdth** attribute to an integer > 0. The restriction on the value of **ocp\_mdatainfo\_wdth** attribute in relation to **ocp\_mdatainfobyte\_wdth** attribute must be obeyed (see the OCP specification for additional information).

### MReqInfo Width

To add the MReqInfo signal in the adapter interface, set the attribute  $ocp\_reqinfo = 1$  and the  $ocp\_reqinfo\_wdth$  attribute to an integer > 0.

#### SDataInfo Width

To add the **SDataInfo** signal in the adapter interface, set the attribute **ocp\_sdatainfo** = **1** and the **ocp\_sdatainfo\_wdth** attribute to an integer > 0. The restriction on the value of **ocp\_sdatainfo\_wdth** attribute in relation to **ocp\_sdatainfobyte\_wdth** attribute must be obeyed (see the OCP specification for additional information).

### SRespInfo Width

To add the **SRespInfo** signal in the adapter interface, set the attribute **ocp\_respinfo** = **1** and the **ocp\_respinfo\_wdth** attribute to an integer > 0.

#### **Burst Extensions**

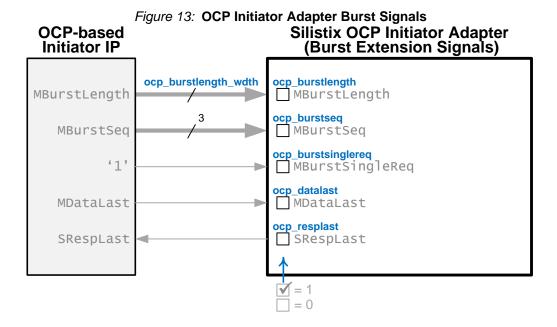

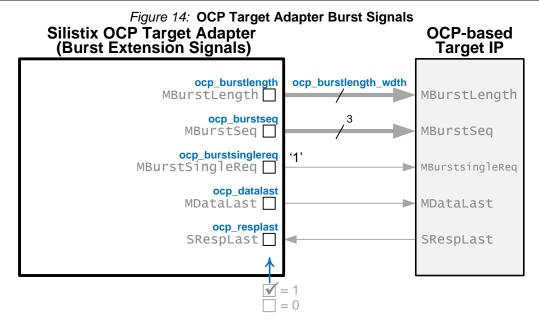

The Burst Extension signals are supported on both the OCP initiator adapter (Figure 13) and the OCP target adapter (Figure 14), with the following restrictions and capabilities.

- The MAtomicLength signal is NOT supported (ocp\_atomiclength = 0).

- The MBlockHeight signal is NOT supported (ocp\_blockheight = 0).

- The MBlockStride signal is NOT supported (ocp\_blockstride = 0).

- The MBurstLength signal is supported and is optional (ocp\_burstlength = 0 or 1) for both initiator and target adapters.

- The MBurstPrecise signal is NOT supported (ocp\_burstprecise = 0). All burst transactions are precise by default.

- The MBurstSeq signal is supported and is optional (ocp\_burstseq = 0 or 1) for both initiator and target adapters. Only the INCR, STRM, WRAP and XOR burst sequences are supported on MBurstSeq. An initiator IP block must ensure that only a supported burst sequence is issued to the initiator adapter. The behaviour of the initiator adapter is undefined if it receives an unsupported burst sequence. Legal settings for the burst sequence enable attributes are as follows

| ocp_burstseq_blck_enable  | 0                    |

|---------------------------|----------------------|

| ocp_burstseq_dflt1_enable | 0                    |

| ocp_burstseq_dflt2_enable | 0                    |

| ocp_burstseq_incr_enable  | <b>0</b> or <b>1</b> |

| ocp_burstseq_strm_enable  | <b>0</b> or <b>1</b> |

| ocp_burstseq_unkn_enable  | 0                    |

| ocp_burstseq_wrap_enable  | <b>0</b> or <b>1</b> |

| ocp_burstseq_xor_enable   | <b>0</b> or <b>1</b> |

■ The MBurstSingleReq signal is supported and is optional (ocp\_burstsinglereq = 0 or 1) for both initiator and target adapters. However the initiator IP block must always drive MBurstSingleReq high during the request phase if it is present on the initiator adapter. The target adapter always drives MBurstsingleReq high during the request phase if it is present. If the adapter does not have MBurstSingleReq then the adapter applies a tie-off value of 1

**38** www.silistix.com (v1.1.3, 31-OCT-2008)

for this signal. In other words the adapters only support single-request/multiple-data burst transactions.

- The MDataLast signal is supported. It is mandatory (ocp\_datalast = 1) for the initiator adapter if burst transactions are supported and optional (ocp\_datalast = 0 or 1) for the target adapter.

- The MDataRowLast signal is NOT supported (ocp\_datarowlast = 0).

- The MReqLast signal is NOT supported (ocp\_reqlast = 0).

- The MReqRowLast signal is NOT supported (ocp\_reqrowlast = 0).

- The SRespLast signal is supported. It is optional (ocp\_resplast = 0 or 1) for the initiator adapter and mandatory (ocp\_resplast = 1) for the target adapter if burst transactions are supported.

- The SRespRowLast signal is NOT supported (ocp\_resprowlast = 0).

Table 13 lists the various burst extension signals on the initiator and target adapters and the associated attributes. Set the signal attribute to 1 to include the signal on the interface. Leave it at the default value 0 to remove the signal from the interface.

If the attribute **ocp\_burstlength=1**, then also define a value for the associated width control attribute, **ocp\_burstlength\_wdth**, which sets the bit width of the **MBurstLength** signal. The **ocp\_burstlength\_wdth** attribute must be an integer, 1 or greater.

| Interface<br>Signal | Silistix<br>Attribute | OCP<br>Parameter | Related Control(s)                | Initiator<br>Default<br>Value | Target<br>Default<br>Value |

|---------------------|-----------------------|------------------|-----------------------------------|-------------------------------|----------------------------|

| MBurstLength        | ocp_burstlength       | burstlength      | ocp_burstlength_wdth              | 0                             | 0                          |

| MBurstSeq           | ocp_burstseq          | burstseq         | N/A                               | 0                             | 0                          |

| MBurstSingleReq     | ocp_burst_singlereq   | burst_singlereq  | ocp_burstsinglereq_<br>tieoff = 1 | 0                             | 0                          |

| MDataLast           | ocp_datalast          | datalast         | N/A                               | 0                             | 0                          |

| SRespLast           | ocp_reslast           | reslast          | N/A                               | 0                             | 0                          |

Table 13: Burst Extensions Signal Attributes

# **Tag Extensions**

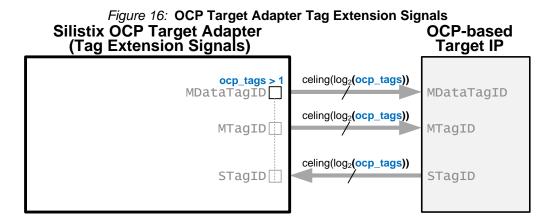

Tag extensions are supported for both the initiator adapter, shown in Figure 15, and the target adapter, shown in Figure 16, with the following restrictions and capabilities.

- The MDataTagID signal is supported and is optional (ocp\_tags = 1 or greater) for both initiator and target adapters.

- The MTagID signal is supported and is optional (ocp\_tags = 1 or greater) for both initiator and target adapters.

- The MTagInOrder signal is NOT supported (ocp\_taginorder = 0).

- The **STagID** signal is supported and is optional (**ocp\_tags** = **1** or greater) for both initiator and target adapters.

The STagInOrder signal is NOT supported ( $ocp\_taginorder = 0$ ).

OCP-based Initiator IP

| MDataTagID | Celing(log<sub>2</sub>(ocp\_tags)) | Celing(lo

All the tag signals are controlled by a single attribute, **ocp\_tags**, as shown in **Table 14**. If the **ocp\_tags** attribute is greater than 1, then all three of the supported tag signals are added to the interface. The width of each signal becomes the number of wires required to represent the number of possible tag states defined by the **ocp\_tags** attribute using binary encoding.

**Initiator Target** Interface **Silistix OCP Default** Default **Attribute Width Control** Signal **Parameter** Value Value **MDataTagID MTagID** tags ceiling[log2(ocp\_tags)] ocp\_tags 1 1 **STagID**

Table 14: Tag Extensions Signal Attributes

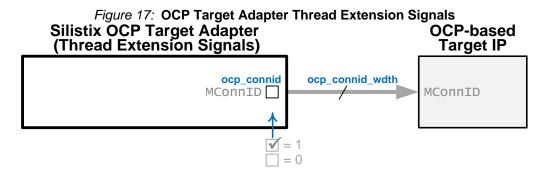

#### **Thread Extensions**

Thread extensions have limited support in the OCP target adapter, shown in Figure 17. There is no thread support for the OCP initiator adapter.

- The MConnID signal is supported by the target adapter and is optional (ocp\_connid = 0 or 1). The initiator adapter does NOT support MConnID (ocp\_mconnid = 0).

- The MDataThreadID signal is NOT supported (ocp\_threads = 1).

- The MThreadBusy signal is NOT supported (ocp\_mthreadbusy = 0).

- The MThreadID signal is NOT supported (ocp\_threads = 1).

- The SDataThreadBusy signal is NOT supported (ocp\_sdatathreadbusy = 0).

- The SThreadBusy signal is NOT supported (ocp\_sthreadbusy = 0).

- The **SThreadID** signal is NOT supported (**ocp\_threads** = **1**).

To add the **MConnID** signal in the target adapter interface, set the attribute **ocp\_connid** =  $\mathbf{1}$  and the **ocp\_connid\_wdth** attribute to an integer > 0. As shown in Table 15, there is no similar support in the initiator adapter.

Table 15: Thread Extensions Signal Attributes

|           |            |           |                 | Initiator | Target  |

|-----------|------------|-----------|-----------------|-----------|---------|

| Interface | Silistix   | OCP       |                 | Default   | Default |

| Signal    | Attribute  | Parameter | Width Control   | Value     | Value   |

| MConnID   | ocp_connid | connid    | ocp_connid_wdth | N/A       | 0       |

# **Sideband Signals**

The OCP adapters only support the asynchronous, active-Low reset inputs as described below. The relevant reset signal appears in Figure 9 or Figure 10.

- The Control signal is NOT supported ( $ocp\_control = 0$ ).

- The ControlBusy signal is NOT supported (ocp\_controlbusy = 0).

- The ControlWr signal is NOT supported ( $ocp\_controlWr = 0$ ).

- The MError signal is NOT supported ( $ocp_merror = 0$ ).

- The MFlag signal is NOT supported ( $ocp_mflag = 0$ ).

- The MReset\_n signal is supported by the initiator adapter and is mandatory (ocp\_mreset = 1). The target adapter does NOT support MReset\_n (ocp\_mreset = 0).

- The SError signal is NOT supported (ocp\_serror = 0).

- The SFlag signal is NOT supported ( $ocp\_sflag = 0$ ).

- The SInterrupt signal is NOT supported (ocp\_interrupt = 0).

- The SReset\_n signal is supported by the target adapter and is mandatory (ocp\_sreset = 1). The initiator adapter does NOT support SReset\_n (ocp\_sreset = 0).

- The **Status** signal is NOT supported ( $ocp_status = 0$ ).

- The StatusBusy signal is NOT supported (ocp\_statusbusy = 0).

- The StatusRd signal is NOT supported (ocp\_statusrd = 0).

Table 16 lists the associated attributes and their default values for the initiator and target adapters.

Table 16: Sideband Signal Attributes

| Interface<br>Signal | Silistix<br>Attribute | OCP<br>Parameter | Related Control | Initiator<br>Default<br>Value | Target<br>Default<br>Value |

|---------------------|-----------------------|------------------|-----------------|-------------------------------|----------------------------|

| MReset_n            | ocp_mreset            | mreset           | N/A             | 1                             | 0                          |

| SReset_n            | ocp_sreset            | sreset           | N/A             | 0                             | 1                          |

# **Test Signals**

The OCP adapters do not support any test signals.

- The ClkByp signal is NOT supported ( $ocp_clkctrl_enable = 0$ ).

- The ScanCtrl signal is NOT supported (ocp\_scanport = 0).

- The Scanin signal is NOT supported (ocp\_scanport = 0).

- The Scanout signal is NOT supported (ocp\_scanport = 0).

- The TCK signal is NOT supported ( $ocp_jtag_enable = 0$ ).

- The TDI signal is NOT supported (ocp\_jtag\_enable = 0).

- The TDO signal is NOT supported (ocp\_jtag\_enable = 0).

- The TestClk signal is NOT supported (ocp\_clkctrl\_enable = 0).

- The TMS signal is NOT supported ( $ocp_itag_enable = 0$ ).

- The TRST\_N signal is NOT supported (ocp\_jtagtrst\_enable = 0).

# **OCP Core RTL Configuration Files**

To be compliant with the OCP-IP specification, a core and its OCP interfaces must be described by an RTL configuration file. The syntax for this file is specified in "Chapter 6: Core RTL Configuration File," found in the Open Core Protocol Specification, Release 2.2. Further details on each statement can be found in the specification.

Several example OCP core RTL configuration files are provided below.

- Default Initiator Adapter

- Default Target Adapter

- Initiator Adapter for MIP32-24K Processor

# **Default Initiator Adapter**

Figure 18 shows the OCP core RTL configuration file for the default initiator adapter. This contains the minimum level of the OCP protocol that must be supported.

Figure 18: Core RTL Configuration File: Default Initiator Adapter

```

version 4.5

module slocp_adapt_ocp_cgp_pmf {

core_id <vendor_code> <core_code> <revision_code> [<description>]

interface ocp bundle ocp2 revision 2 {

interface_type slave

net Clk

port clk

port nreset

port ocp_MAddr

net MReset_n

net MAddr

port ocp_MCmd

net MCmd

port ocp_MData

net MData

port ocp_MDataValid

net MDataValid

port ocp_SCmdAccept

net SCmdAccept

port ocp_SData

net SData

port ocp_SDataAccept

port ocp_SResp

net SDataAccept

net SResp

prefix ""

param datahandshake

1

{width 32}

{tie_off 1}

param addr

param burstsinglereq

param cmdaccept

1

param dataaccept

param data_wdth

64

param mdata

1

param resp

1

param sdata

param mreset

param sreset

} # End of interface ocp

} # End of module slocp_adapt_ocp_cgp_pmf

```

**44** www.silistix.com (v1.1.3, 31-OCT-2008)

### **Default Target Adapter**

Figure 19 shows the OCP core RTL configuration file for the default target adapter. This contains the minimum level of the OCP protocol that must be supported.

Figure 19: Core RTL Configuration File: Default Target Adapter

```

version 4.5

module slocp_adapt_cgp_pmf_ocp {

core_id <vendor_code> <core_code> <revision_code> [<description>]

interface ocp bundle ocp2 revision 2 {

interface_type master

net Clk

net SReset_n

port clk

port nreset

port ocp_MAddr

net MAddr

port ocp_MCmd

net MCmd